俹俴俴傪愙懕偡傞

偦偺侾丂僕儍儞僷僙僢僥傿儞僌埲奜偺僋儘僢僋偼嫙媼壜擻偐丠

儅僓乕儃乕僪偵傛偭偰偼丄俆侽乛俇侽乛俇俇俵俫倸埲奜偺僋儘僢僋愝掕偑側偄乮弌棃側偄乯儌僨儖偑偁傞丅

杮摉偵弌棃側偄偺偐丠偦偺曈傝傪扵偭偰傒傛偆丅

壗屘偦傫側偙偲傪峫偊傞偐偲偄偆偲丄椺偊偽侾俉侽俵俫倸偱摦嶌壜擻側俠俹倀偺応崌偵丄俇侽俵俫倸偺俁攞儌乕僪偲俉侽俵俫倸偺俀攞儌乕僪偱偺僷僼僅乕儅儞僗傪挷傋傞偲俉侽俵俫倸偺俀攞儌乕僪偺曽偑俠俹倀僋儘僢僋偑掅偄偵傕娭傢傜偢僷僼僅乕儅儞僗偑崅偄偐傜偩丅

傕偭偲傕丄儅僓乕儃乕僪帺懱偑俉侽俵俫倸偱摦嶌偟側偔偰偼堄枴柍偄偑丅

堦斒揑側僋儘僢僋嫙媼梡俬俠偼丄暋悢偺廃攇悢偵曄峏偱偒傞傛偆偵嶌傜傟偰偄傞丅

偦偺拞偱丄儅僓乕儃乕僪偵昁梫側廃攇悢愝掕傪峴偆抂巕偺傒偑僕儍儞僷傗廃攇悢愗傝懼偊梡僗僀僢僠偵愙懕偝傟偰偄傞偺偩丅

巆傝偺廃攇悢愝掕梡抂巕偼丄揹尮偐俧俶俢偵屌掕偝傟偰偄傞丅

僋儘僢僋嫙媼梡俬俠偺丆俬俠傪摦嶌偝偣傞偨傔偺揹尮抂巕偼侾乣俀杮丄俧俶俢偼侾杮掱搙偱偁傞丅

偩偐傜丄偦傟埲奜偵傕揹尮傗俧俶俢偵愙懕偝傟偰偄傞抂巕偑桳傟偽偦傟偼廃攇悢愝掕梡偱桳傞偙偲偑峫偊傜傟傞丅

偦偙偱丄偦傟傜揹尮傗俧俶俢偵愙懕偝傟偰偄傞抂巕傪婎斅偐傜晜偐偣偰俧俶俢偵愙懕偟偨傝揹尮偵愙懕偟偨傝偟偰廃攇悢偑曄傢傞偐妋擣偡傞偺偩丅

巹偑宱尡偟偨俬俠偱偼丄俬俠撪晹偱僾儖傾僢僾偝傟偰偄偨偐傜抂巕傪僆乕僾儞偵偡傞偐丆俧俶俢偵偡傞偐偱廃攇悢偑曄峏偱偒偨丅

偙偺曽朄偱丄巹偼俬俠傪夡偟偨偙偲偼側偄偑夡傟傞壜擻惈傕偁傞丅

俽俷俹乮昞柺幚憰宆乯偱偼丄揹婥揑攋夡偺傒側傜偢暔棟揑攋夡乮懌偑儌僎偪傖偆偲偐乯傕桳傞偺偱拲堄偝傟偨偄丅

偙偺傛偆側幚尡偱傕岲傒偺廃攇悢偑尒偮偐傜側偐偭偨応崌偼丄俹俴俴傪愙懕偡傞偺偑椙偄偩傠偆丅

俹俴俴偲偼堦斒揑屇傃柤偱偁偭偰丄偦傟帺懱偼敪怳婍傪堄枴偡傞棯岅偱偼側偄丅

俹倛倎倱倕丂?

枴鐱釨鍮鉈鉄丅

枴鐱鐱锜丆暍棦悽?錊?

俹俴俴傪夝愢偡傞偲挿偔側傞偺偱丄偙偙偱偼俹俴俴亖帺桼側廃攇悢偑旕忢偵埨掕偵嫙媼偱偒傞敪怳婍丆偲偟偰愢柧偡傞丅

偙傟偑丄Nifty 偺 FEXT 偱愝寁惢嶌偝傟偨俹俴俴丅

嵍偺婎斅偑廃攇悢愝掕梡偱丄俈僙僌俴俤俢偵傛傞廃攇悢昞帵偑晅偄偰偄傞丅

敪怳晹偼丄塃懁偺彫宆婎斅丅

偦偙偐傜偼摨幉働乕僽儖偱僋儘僢僋傪嫙媼偡傞丅

偙偺FEXT PLL偼丄揹尮嫙媼傕俥俢俢偲摨偠僐僱僋僞偱娙扨偩丅

偱偼丄偳偙偵僋儘僢僋傪嫙媼偡傟偽傛偄偺偐丠係俉俇帪戙偵偼丄侾宯摑偺僋儘僢僋偺傒偱椙偐偭偨偐傜俠俹倀偺僋儘僢僋抂巕偵俹俴俴偺弌椡傪嫙媼偡傞傛偆側傗傝曽偱椙偐偭偨丅

偟偐偟丄Pentium偱偼僠僢僾僙僢僩偵俠俹倀僋儘僢僋偺侾乛俀傪嫙媼偟偰傗傜側偔偰偼側傜側偄応崌偑偁傞丅

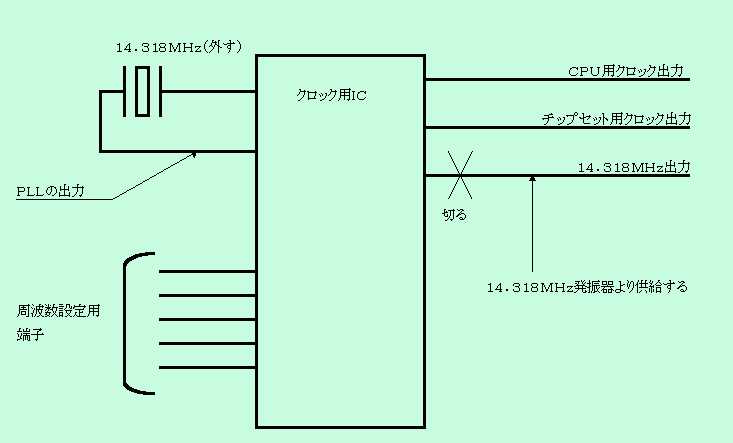

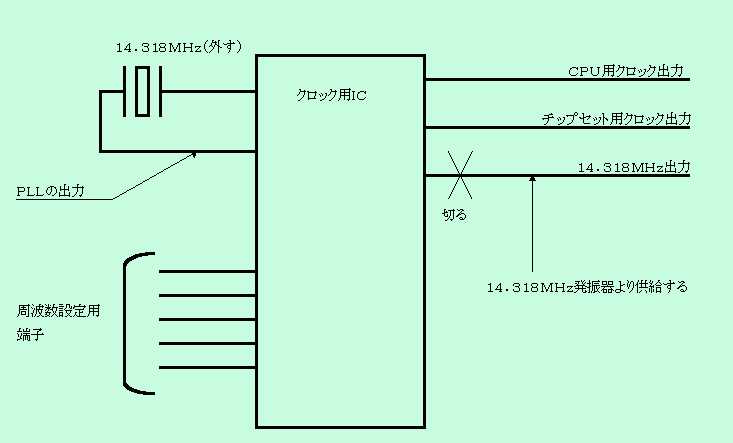

偦偙偱丄僋儘僢僋嫙媼梡俬俠偺婎弨偲側偭偰偄傞侾係丏俁侾俉俵俫倸偺悈徎怳摦巕偺戙傢傝偵俹俴俴傪愙懕偡傞偺偩丅

偮傑傝丄捠忢侾係丏俁侾俉俵俫倸偱俇侽俵俫倸偺摦嶌僋儘僢僋偑摼傜傟傞応崌偵丄侾係丏俁侾俉俵俫倸偵戙偊偰俀侽俵俫倸傪擖傟傞偲丄栺俉俁丏俉俵俫倸偺僋儘僢僋偑摼傜傟傞寁嶼偩丅

偨偩偟丄侾係丏俁侾俉俵俫倸偦偺傕偺傕嫙媼偟側偔偰偼偄偗側偄僨僶僀僗偑偁傞偐傜丄偦傟偵偼暿偺敪怳婍偐傜侾係丏俁侾俉俵俫倸傪擖傟偰傗傜側偗傟偽偄偗側偄丅

偦偺僨僶僀僗偼庡偵僞僀儅娭學偩丅

傕偆堦偮丄僆儞儃乕僪俬乛俷偺俥俢俠乛俫俢俠偵偼俀係俵俫倸乮侾俀俵俫倸偺応崌傕偁傞乯傪昁梫偲偡傞暔偑懡偄丅

偦傟傜偺僨僶僀僗偵俀係俵俫倸偺悈徎怳摦巕偑愙懕偝傟偰偄傟偽傛偄偑丄偦傟傑偱傕僋儘僢僋嫙媼梡俬俠偑傗偭偰偄傞偲側傞偲丄偦傟傕暿偵梡堄偟側偔偰偼偄偗側偔側傞丅

偙偺曈傝偼丄奺帺挷傋傞偟偐曽朄偼側偄丅

媡偵丄偙傟傜偑暘偐傜側偄傛偆側傜僋儘僢僋傾僢僾偡傋偒偱偼側偄偲巚偆丅